OVERVIEW

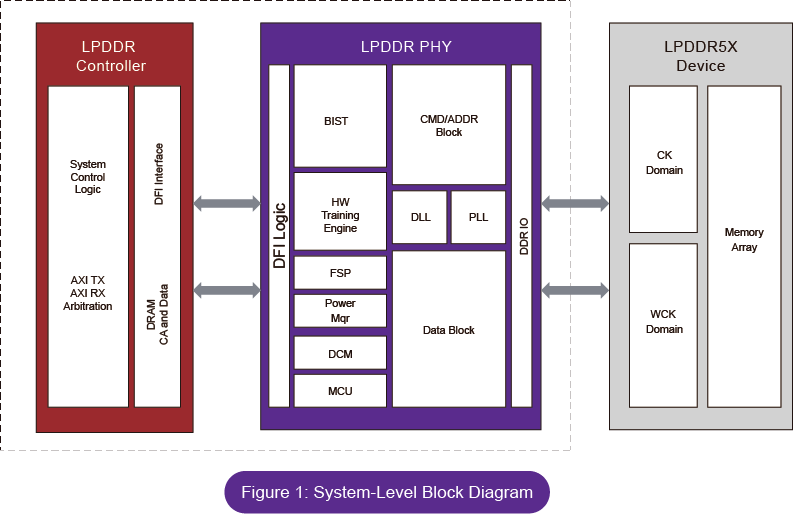

MSquare's LPDDR5X/4X PHY is a transceiver physical layer IP interface solution designed for ASICs and SOCs. Compatible with the universal IP protocol DFI 5.0, it operates at data rates up to 8533Mbps with a 16-bit data width per channel. With flexible configuration options, the LPDDR5X/4X PHY supports a variety of mobile applications using LPDDR5X, LPDDR5, and LPDDR4X SDRAMs. Featuring a hybrid analog/digital architecture, MSquare's IP delivers low power consumption, compact footprint, and robust performance, making it well-suited for LPDDR5X/4X applications.

HIGHLIGHTS

Compatible with JEDEC standards LPDDR4X , LPDDR5 and LPDDR5X SDRAMs

Supports for data transfer rate up to 8533Mbps

DFI 5.0 for PHY and controller interfaces

Supports both firmware-based training and hardware-based training

Supports multiple gears of DFS

High performance, low jitter DDR IO

Single Tap DFE for Channel Robustness

Supports 4 trained frequencies

User-customizable arbiter (scheduler)

Compliant with JEDEC standards JESD209-4D and JESD209-5B