OVERVIEW

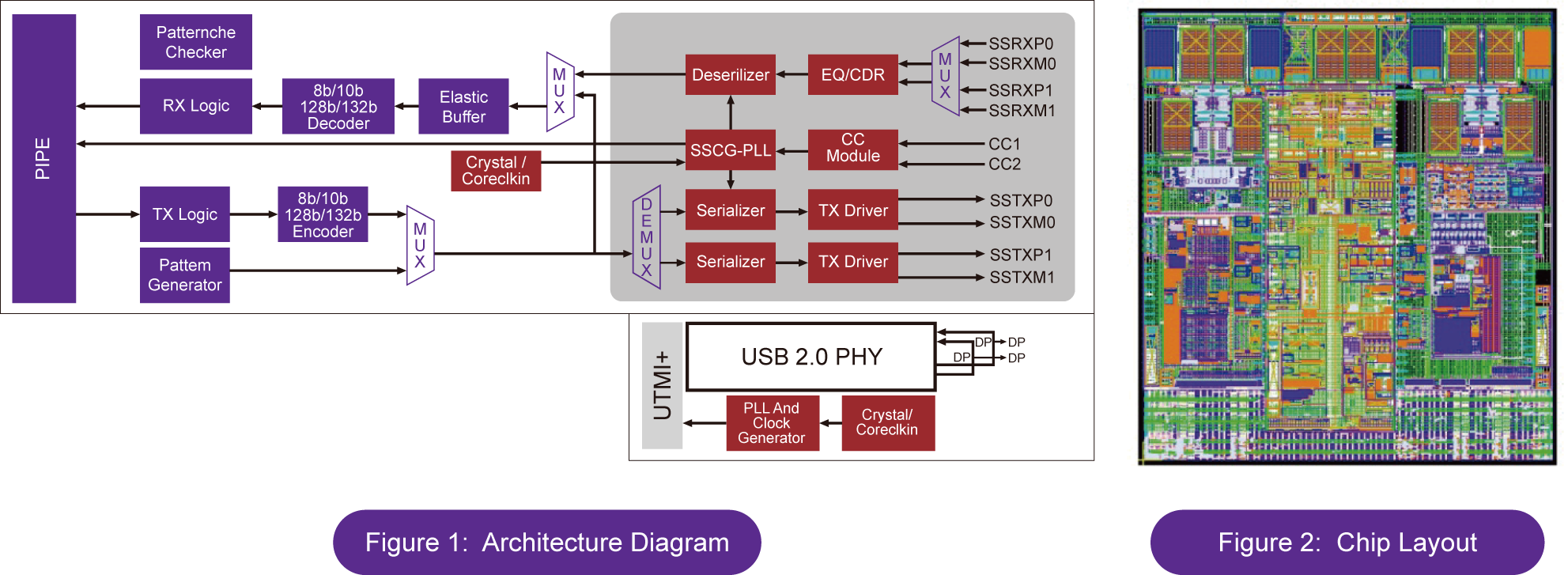

MSquare's USB 3.2 PHY IP is designed based on the USB 3.2 Gen2x1 and USB 2.0 specifications from the USB Implementers Forum and delivers bandwidth up to 10Gbps. This high bandwidth capability is particularly beneficial for consumer and industrial video applications, as well as display, docking, cloud computing, and automotive applications.

As a leading supplier of USB IP, MSquare offers customers low-power, compact, and high-performance IPs featuring a unique hybrid analog/digital architecture. This IP supports all USB functions, including transceivers for 10G, 5G, 480M, 12M, and 1.5Mbps. It provides complete deliverables that simplify SoC integration and silicon validation. Available in a wide variety of process nodes from 40nm to 6/7nm, this IP features a compact die size and low pad count, enhancing product competitiveness in the USB market.

HIGHLIGHTS

Fully compliant with USB 3.2 Gen2x1 featuring PIPE 4.3 and USB 2.0 with a UTMI+ interface

Supports host, peripheral, and dual-role applications

Supports 10/12/25/30/19.2/24/27/40MHz crystal oscillators or clock inputs

Supports TX 3-Tap FFE and RX CTLE+1-Tap DFE for SS+

Integrates an active switch to support orientation-less connections with the USB Type-C connector

Provides an auxiliary CC module IP for USB Type-C related functions

Offers robust BIST functions for mass production tests

Supports a crystal pad for clock source, compatible with MSquare's XTAL module IP

Supports OTG applications, compatible with MSquare's IDPAD module IP

Available in 7nm, 12nm, 16nm, 28nm, and 40nm processes

Supports both wire-bond and flip-chip package types